随着AI大模型等应用爆发式发展,智能算力需求激增,算力已成为战略资源和科技竞争的焦点。芯片作为算力的物理载体,其性能决定了算力输出的质量与数量。先进封装作为后摩尔时代提升芯片性能的关键环节,正成为算力竞争中的核心赛道。

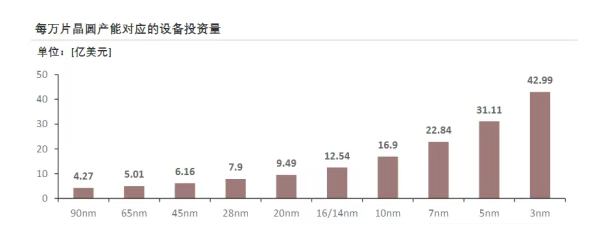

摩尔定律指集成电路上容纳的晶体管数目约每18个月便会增加一倍,但随着晶体管特征尺寸缩小到10nm以下,量子隧穿效应导致漏电愈发严重,基于摩尔定律的芯片研发和制造成本也会呈几何倍数增加,摩尔定律延续遇到瓶颈。先进封装能够在不缩小制程节点的背景下,仅通过改进封装方式就提升芯片性能,是后摩尔时代延续芯片性能提升的重要手段之一。#AI算力

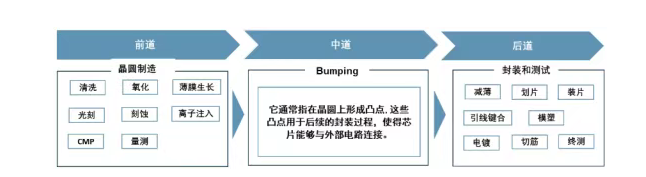

在芯片制造领域,完整的半导体生产过程可分为前道、中道、后道三个主要阶段。

前道:前道工艺主要涉及晶圆制造,这是在空白的硅片上完成电路加工的过程,包括光刻、刻蚀、薄膜生长、离子注入、清洗、CMP(化学机械抛光)和量测等工艺步骤。这个阶段的目标是在硅片上形成晶体管和其他有源器件,以及多层互连结构。#芯片封装

中道:中道是介于晶圆制造和封装测试之间的一个环节,有时也被称作“Bumping”。它通常指的是在晶圆上形成的凸点(Bumps),这些凸点用于后续的封装过程,使得芯片能够与外部电路连接。中道制造随着高密度芯片需求的增长而变得越来越重要,尤其是在倒装芯片(Flip-Chip)技术中。

后道:后道工艺主要涉及封装和测试。包括减薄、划片、装片、引线键合、模塑、电镀、切筋/成型和终测等步骤。这个阶段的目标是将圆形的硅片切割成单独的芯片颗粒,完成外壳封装,并进行电气测试以确保性能符合标准。

(资料来源:CSDN,东兴证券研究所)

芯片封装为半导体制造后道工艺中的核心环节,是指用特定材料、工艺技术对芯片进行安放、固定、密封,并将芯片上的接点连接到封装外壳上的工艺流程。芯片封装的核心作用是将脆弱的晶圆切割后的裸芯片转化为具备机械强度、电气性能、散热能力及可靠性的终端产品,同时实现芯片与外部系统的兼容性与功能性接口。

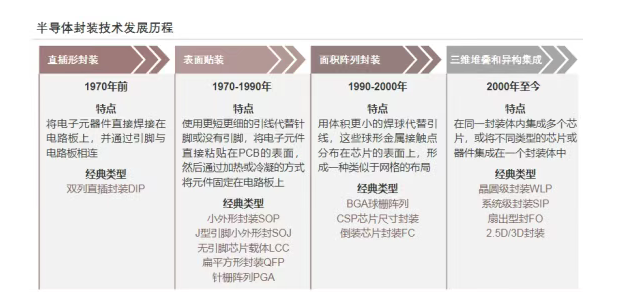

半导体封装技术的发展大致可分为四个阶段,分别为:1)第一阶段(1970年前):主要使用直插形封装,如双列直插封装(DIP),通过引脚与电路板连接;2)第二阶段(1970-1990年):引入表面贴装技术,包括多种封装形式如SOP、SOJ、LCC、QFP和PGA,通过更短更细的引线或无引脚设计实现更高的集成度;3)第三阶段(1990-2000年):采用面积阵列封装,如BGA、CSP和FC,通过焊球代替引线,提高密度和可靠性;4)第四阶段(2000年至今):发展到三维堆叠和异构集成,如WLP、SIP、2.5D/3D封装,进一步提升集成度和性能。目前全球封装技术所处的第四阶段,即先进封装阶段。

(资料来源:《先进封装技术的发展与机遇》,头豹研究院)

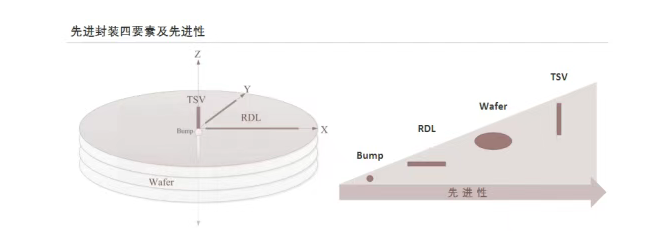

先进封装以内部封装工艺的先进性为评判标准。先进封装的四要素是指RDL(再布线层)、TSV(硅通孔)、Bump(凸块)、Wafer(硅晶圆),任何一款封装,如果具备了四要素中的任意一个,都可以称之为先进封装。

在先进封装的四要素中,Bump用来取代传统封装中的引线键合,主要起几面电气互联和应力缓冲的作用,当前先进封装无一例外均使用了Bump工艺;RDL起着XY平面电气延伸的作用,Interposer(中介层,以硅为主)也发挥相似作用,主要应用于晶圆级封装和2.5D/3D封装技术;Wafer作为集成电路的载体以及RDL和TSV的介质和载体,在2.5D封装中用于制作硅基板,也在WLP晶圆级封装中作为承载介质,用于在晶圆级完成RDL、凸块等封装工艺;TSV起着Z轴电气延伸的作用,是2.5D/3D封装技术实现的主要途径。从技术推出时间前后及先进性程度来看,排序为Bump、RDL、Wafer、TSV。

(资料来源:《SiP与先进封装技术》,《人工智能芯片先进封装技术》,头豹研究院)

相较于传统封装,先进封装拥有更高的内存带宽、能耗比、性能、更薄的芯片厚度,可实现多芯片、异质集成、芯片之间的高速互联。

(资料来源:《SiP与先进封装技术》,《人工智能芯片先进封装技术》,头豹研究院)

03-1 FC(倒装芯片封装)

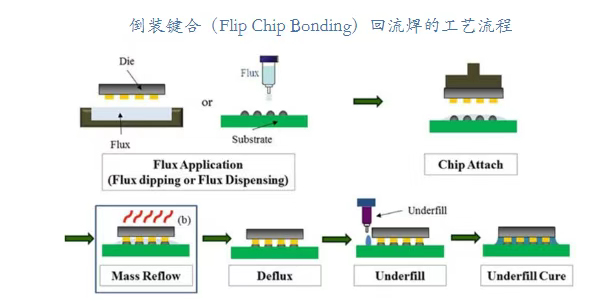

FC(倒装芯片封装)是将芯片功能区朝下以倒扣的方式背对着基板,通过焊料凸点(Bump)与基板进行互联的封装技术。基础的倒装芯片采用回流焊作为键合方案,此外,还有热压焊、超声焊和胶粘连接等方案。倒装芯片起源于20世纪60年代,由IBM率先研发,是发展时间最长的先进封装技术。

(资料来源:雪域资本、华安证券研究所)

03-2 WLP(晶圆级芯片封装)

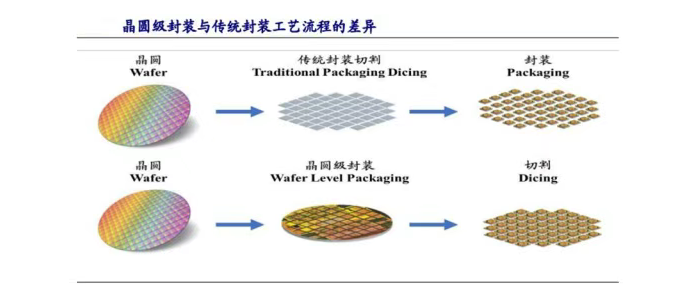

WLP(晶圆级芯片封装)切割晶圆与封装的先后顺序与传统方式大不相同。在传统晶圆封装中,是将成品晶圆切割成单个芯片,然后再进行黏合封装。不同于传统封装工艺,晶圆级封装是在芯片还在晶圆上的时候就对芯片进行封装,保护层可以黏接在晶圆的顶部或底部,然后连接电路,再将晶圆切成单个芯片。

(资料来源:Cadence)

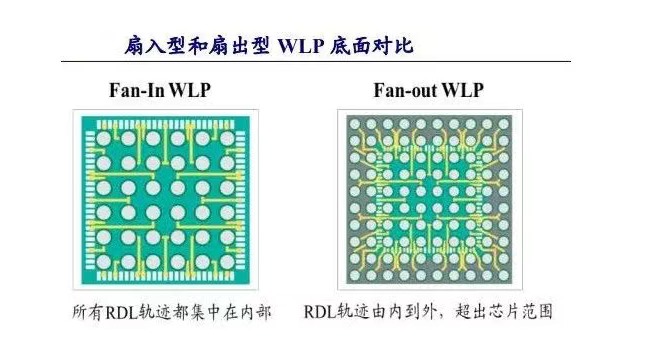

晶圆级芯片封装分为两种主要类型:扇入型与扇出型晶圆级封装,两者的主要区别在于如何合并重布线层(RDL)。在扇入型,RDL走线向内布线,面积受到限制,约200个I/O和0.6mm将达到上限。而在扇出型中,通过扩展封装的可用面积,RDL走线可以向内和向外布线,从而实现更薄的封装和更多的I/O。

(资料来源:ASE,开源证券研究所)

03-3 2.5D/3D封装

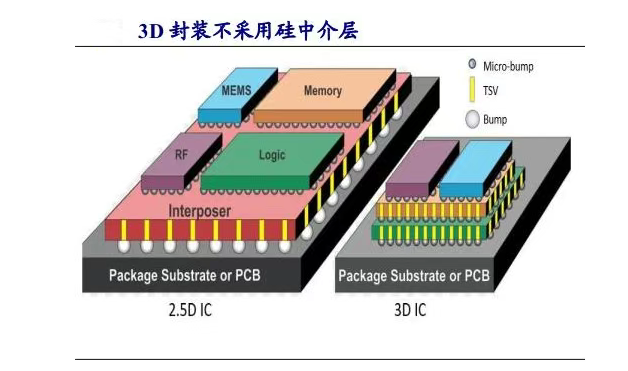

2.5D封装是在2D封装结构的基础上,芯片与封装载体之间加入硅中介层进行打孔和布线。通过利用硅通孔连接其上、下表面的金属,多采用倒装芯片组装工艺。和2D结构封装相比,采用2.5D结构封装的产品容量和性能更高。3D与2.5D封装的主要区别在于,2.5D是在中介层上进行打孔和布线的,而3D封装是将芯片与芯片直接堆叠。在高性能计算芯片中,通过3D堆叠技术可以扩大内存芯片的容量、提升传输带宽,同时由于堆叠中引线的减少,大大降低了芯片中因数据传输造成的不必要的能量损耗,因此采用TSV工艺的3D IC大量运用于存储器(SRAM、DRAM、Flash)、GPU、CPU等多种高端应用领域。

(资料来源:Semiconductor Engineering)

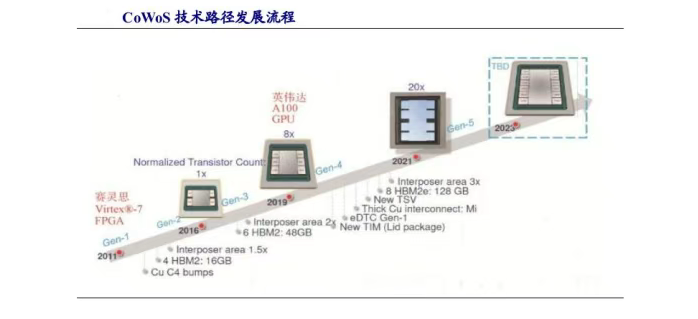

CoWoS(基板上的晶圆级芯片封装)是台积电的2.5D封装技术,通过硅中介层多个芯片集成到同一基板上,实现异构计算。该技术分为CoWoS-S(硅中介层)、CoWoS-R(重新布线层中介层)和CoWoS-L(混合中介层)。从第三代开始,CoWoS由同质集成转变为异质集成。第五代芯片不仅对逻辑与内存进行了改进,还针对硅中介层的RDL、TSV进行改进,在硅中介层加入了eDTC(嵌入式深沟槽电容器)以进一步稳定电源系统。

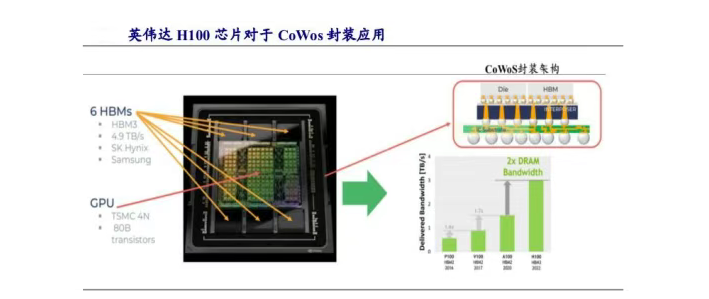

CoWoS先进封装技术主要应用于AI算力芯片及HBM领域。英伟达是CoWoS主要需求大厂,在台积电的CoWoS产能中,英伟达占整体供应量比重超过50%。Hopper系列的A100和H100、Blackwell Ultra 均使用台积电CoWoS封装工艺。

03-4 Chiplet封装

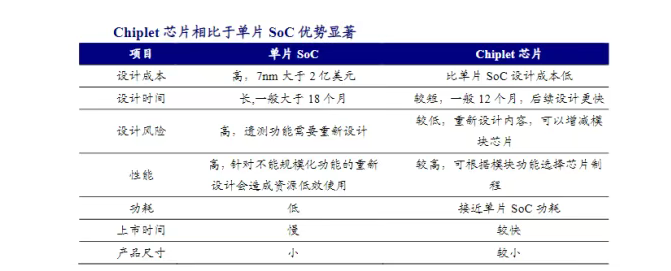

Chiplet又称芯粒或者小芯片,通过die-to-die内部互联技术实现多个模块芯片与底层基础芯片封装在一起,形成系统芯片,以实现新形式的IP复用。Chiplet允许更多的设计灵活性,更快的上市时间,更好的产量,比单片SoC方案更具经济效益。具体优势体现在三个方面:1)大幅提高大芯片良率;2)降低设计的复杂度和设计成本;3)降低芯片制造成本。

全球先进封装市场参与者包括IDM类厂商、Foundry类厂商及OSAT类厂商(外包)。头部厂商在先进封装上普遍采用“大平台+技术分支”的架构,覆盖晶圆级、2.5D/3D封装等技术,形成覆盖全场景的封装解决方案。国际头部OSAT厂商、晶圆代工厂及IDM企业正加速在扇出型封装(Fan-out)、2.5D/3D先进封装等关键技术领域构建专利壁垒,通过持续研发创新产品、推动量产落地,进一步巩固其行业领先地位。

中国大陆头部OSAT厂商通过自主研发和兼并收购,已基本形成先进封装的产业化能力。中国大陆封测三大厂长电科技、通富微电和华天科技均采用平台化战略,覆盖从消费电子到AI芯片的全场景。

根据OSAT厂商的技术特点、营收规模、客户资源三大维度进行梯队划分,

全球第一梯队厂商有日月光和安靠科技;

第二梯队厂商有长电科技、通富微电、华天科技、力成科技、盛合晶微等;

第三梯队厂商有京元电子、南茂科技、智路封测、韩亚微(韩国)、甬矽电子、汇成股份、科阳半导体、天成先进等。

撰文/策金研究 编辑/颜晓峰 排版/陈玲丽